CPC Definition - Subclass G06F

This place covers:

Electrical arrangements or processing means for the performance of any automated operation using empirical data in electronic form for classifying, analyzing, monitoring, or carrying out calculations on the data to produce a result or event.

This place does not cover:

Computer systems based on specific computational models |

Attention is drawn to the following places, which may be of interest for search:

Program-control systems | |

Digital computers in which all the computation is effected mechanically | |

Computers in which a part of the computation is effected hydraulically or pneumatically | |

Computers in which a part of the computation is effected optically | |

Self-contained input or output peripheral equipment | |

Computer displays | |

Impedance networks using digital techniques |

In this place, the following terms or expressions are used with the meaning indicated:

Handling | includes processing or transporting of data. |

Data processing equipment | An association of an electric digital data processor classifiable under group G06F 7/00, with one or more arrangements classifiable under groups G06F 1/00- G06F 5/00 and G06F 9/00- G06F 13/00. |

This place covers:

Details not covered by groups G06F 3/00-G06F 13/00 and G06F 21/00.

This place does not cover:

Architectures of general purpose stored program computers |

Attention is drawn to the following places, which may be of interest for search:

Evaluating functions by calculating only | |

Generating sawtooth or staircase waveforms |

Attention is drawn to the following places, which may be of interest for search:

Generation of pulse trains in general |

This place covers:

Generation and/or distribution of clock signal(s) within a computer system.

This place covers:

Distribution of clock signal(s) within a computer system, in a typical case the goal to be achieved is to minimize the skew.

This place covers:

Clock distribution wherein the clock signal(s) are distributed entirely optically or partially optically and partially electrically.

Used also for hoods protecting displays of portable computers.

Used also for accessories attached on displays of portable computers.

This place covers:

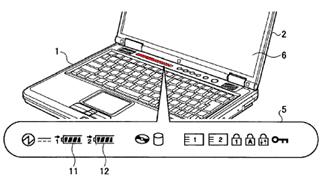

Portable computers in the sense of computers able to be used as standalone computers with their own integrated user interface and designed to be carried by hand (e.g. hand held computers or laptop computers) or worn on the user's body (wearable computers).

Docking stations and extensions associated with the portable computers which may be mechanically attached to them.

This place does not cover:

Cooling arrangements for portable computers | |

Constructional details or arrangements for pocket calculators, electronic agendas or books | |

Constructional details of portable telephone sets: with several bodies |

Attention is drawn to the following places, which may be of interest for search:

Anti-theft locking devices | |

Constructional details of cameras | |

Hand held scanners | |

Personal calling arrangements, i.e. paging systems or devices, i.e. pagers | |

Casing of remote controls | |

Telephone sets including user guidance or feature selection means facilitating their use | |

Cordless telephones | |

Cameras or camera modules comprising electronic image sensors |

In this field, main mechanical aspects of the housing (single housing, foldable or sliding housings) are classified in G06F 1/1615 - G06F 1/1626, while all the other constructional details (enclosure details, display, keyboard, integrated peripherals, etc) are classified in G06F 1/1633 in complement to this main aspect.

In patent documents, the following words/expressions are often used as synonyms:

- "laptop", "palmtop" and "PDA"

- " cell phone", "mobile phone" and "smart phone"

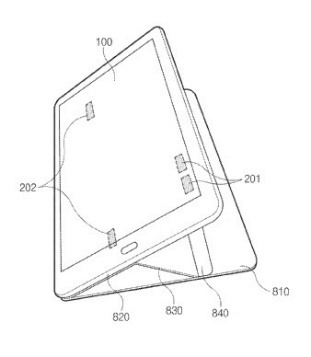

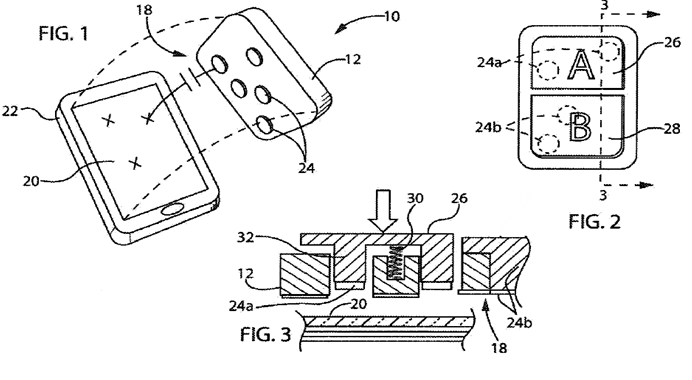

This place covers:

Portable computers having a plurality of enclosures which can't be classified in anyone of the subgroups, e.g. multiple enclosure with loose mechanical link (single wire, expandable or/and flexible link, rollable part), computer split in several housings with no mechanical connection and wirelessly connected, complex mechanical link with multiple degrees of freedom.

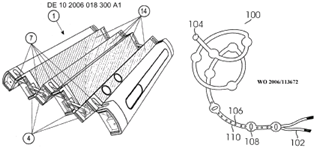

Illustrative examples:

This place does not cover:

Constructional details of portable telephones comprising a plurality of mechanically joined movable body parts |

Attention is drawn to the following places, which may be of interest for search:

Foldable portable telephones |

This place covers:

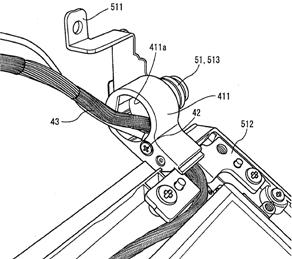

Also when the hinging part is composed of two parallel rotation axes.

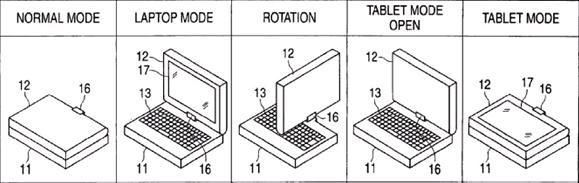

This place covers:

Reversing the orientation done either by rotating along the X or Y axis or by detaching the display and attaching it in the reverse orientation. Illustrative example:

This place covers:

Illustrative examples of subject matter classified in this group:

Additionally rotation around an axis common to the plane they define but perpendicular to their common side, e.g. reversing the relative orientation along an axis common to both planes but not along their sides (which would be then a folding axis).

This place does not cover:

Reversing the face orientation of the screen of a folding flat display |

Attention is drawn to the following places, which may be of interest for search:

Rotatable portable telephones |

This place covers:

Portable computers linked by a mechanism allowing translation of one housing relatively to the other housing.

Attention is drawn to the following places, which may be of interest for search:

Slidable portable telephones |

This place covers:

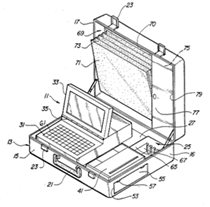

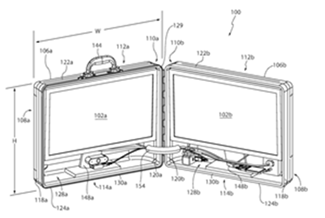

Portable enclosures allowing the transport of the portable computer together with other peripherals.

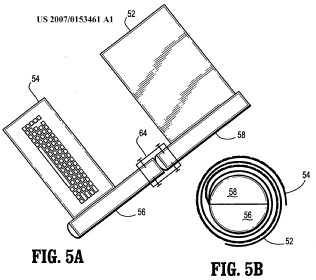

Illustrative examples of subject matter classified in this place:

1.

2.

Figure 2 illustrates a portable system for carrying a monitor and a computing device in a case.

In the context of subclass A45C, storing is understood as to refer to putting or keeping something in a receptacle for future use.

Receptacles for storing portable audio devices, portable handheld communication devices or portable computing devices where the device must be removed for use are classified in A45C 11/001, A45C 11/002 and A45C 11/003, respectively.

Holders or carriers being worn by a user for portable audio devices, portable handheld communication devices and portable computing devices to facilitate transporting or carrying, where the device is not in use or being passively used, are classified in groups A45F 5/1508, A45F 5/1516 and A45F 5/1525, respectively.

Protective covers or auxiliary enclosures for mobile phones that are intended to hold the device during use without hampering the telephonic functions are classified in H04M 1/0203.

Constructional features, like venting or EMI shielding means, of electronic housings not characterised by the inner electronic arrangements are classified in H05K 5/00.

Attention is drawn to the following places, which may be of interest for search:

Protective covers or auxiliary enclosures for portable computers | |

Bags | |

Receptacles for storing portable computing devices, e.g. laptops, tablets or calculators | |

Holders or carriers for portable computing devices, e.g. laptops, tablets or calculators | |

Stands with or without wheels as supports for apparatus | |

Arrangements for carrying or protecting portable transceivers in general |

Enclosures for carrying portable computers with peripheral devices, like a printer or a charger, are classified in G06F 1/1628.

G06F 1/1629 relates to protective covers or auxiliary enclosures for portable computers that are intended to hold the device during use. Details related to functional adaptations of the enclosures, e.g. to provide protection against EMI, shock or water are identified by allocating further classification in G06F 1/1656 or subgroups.

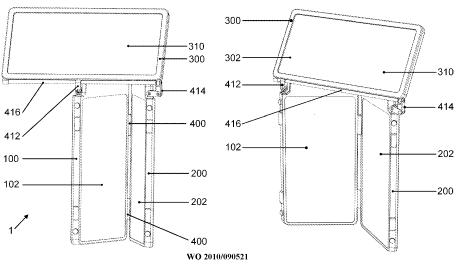

This place covers:

Protective covers or auxiliary enclosures for portable computers that are intended to hold the device during use without hampering said use. The covers or enclosures for portable computers are in principle detachable but intended to remain on the computer during use.

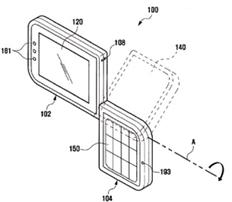

Illustrative example of subject matter classified in this place:

1a.

1b.

1c.

Protective covers or auxiliary enclosures for portable computers that are intended to hold the device during use are classified in G06F 1/1629 while receptacles for storing portable audio devices, portable handheld communication devices or portable computing devices where the device must be removed for use are classified in A45C 11/001, A45C 11/002 and A45C 11/003, respectively.

In the context of subclass A45C, storing is understood as to refer to putting or keeping something in a receptacle for future use.

Holders or carriers being worn by a user for portable audio devices, portable handheld communication devices and portable computing devices to facilitate transporting or carrying, where the device is not in use or being passively used, are classified in groups A45F 5/1508, A45F 5/1516 and A45F 5/1525, respectively.

Protective covers or auxiliary enclosures for mobile phones that are intended to hold the device during use without hampering the telephonic functions are classified in H04M 1/0203.

Constructional features, like venting or EMI shielding means, of electronic housings not characterised by the inner electronic arrangements are classified in H05K 5/00.

Supports for positioning or steadying a device relative to a person with the intent of using the device are classified in F16M 13/04.

This place does not cover:

Enclosures for carrying portable computers with peripheral devices | |

Receptacles for storing portable computing devices, e.g. laptops, tablets or calculators |

Attention is drawn to the following places, which may be of interest for search:

Receptacles for storing portable audio devices like headphones or digital music players | |

Receptacles for storing portable handheld communication devices, e.g. pagers or smart phones | |

Holders or carriers for portable audio devices | |

Holders or carriers for portable handheld communication devices | |

Holders or carriers for portable computing devices | |

Supports for positioning or steadying a device relative to a person | |

Arrangements for carrying or protecting portable transceivers | |

Protective covers or auxiliary enclosures for portable telephones | |

Casings, cabinets or drawers for electric apparatus |

Enclosures for carrying portable computers with peripheral devices, like a printer or a charger, are classified in G06F 1/1628.

Details related to functional adaptations of the enclosures, e.g. to provide protection against EMI, shock or water are identified by allocating further classification in G06F 1/1656 or subgroups.

This place covers:

Portable computers, e.g. smart watches, whereby the portable computer itself is worn by a user.

Carrying devices like bands or straps worn on the user to which a computer is attached for facilitating transport or carrying when the computer is not in use or being passively used, e.g. belt clip with means for retaining a tablet, the tablet being removed from the belt clip for use, is classified in A45F 5/1525.

Attention is drawn to the following places, which may be of interest for search:

Garments adapted to accommodate electronic equipment | |

Fastening articles to garments | |

Holders or carriers for portable computing devices, e.g. laptops, tablets or calculators |

This place covers:

Expansions which are directly attached to portable computers, including supplementary battery packs external to the housing, port replicators and cradles for PDAs.

This place does not cover:

Standard wired or wireless peripherals such as keyboards, printers or displays which are not mechanically linked to a portable computer |

Attention is drawn to the following places, which may be of interest for search:

Mounting in a car | |

Locking against unauthorized removal | |

Battery charging cradles | |

PCMCIA cards |

In patent documents, the following words/expressions are often used as synonyms:

- "docking station", "cradle" and "port replicator"

Attention is drawn to the following places, which may be of interest for search:

Constructional details or arrangements of portable computers specific to the type of enclosures | |

Mounting of specific components of portable telephones |

Attention is drawn to the following places, which may be of interest for search:

Computer power supply in general | |

Details of mounting batteries in general | |

Portable telephones battery compartments |

Attention is drawn to the following places, which may be of interest for search:

Constructional details related to the housing of computer displays in general | |

Accessories mechanically attached to the display housing portion of portable computers | |

Portable telephones display |

This place does not cover:

Including at least an additional display |

Should be used when the displays are used in combination as a virtual single display area where the displayed image is split over the display screens.

This place does not cover:

Movement typologies |

Attention is drawn to the following places, which may be of interest for search:

Touchpads integrated in a laptop or similar computer | |

Secondary touch screen |

This place does not cover:

Constructional details or arrangements related to integrated I/O peripheral being a secondary touch screen used as control interface, e.g. virtual buttons or sliders |

This place covers:

Typically very small displays disposed on the back of the main display for indicating time, alerts or battery level or small status displays near the hinge above the keyboard. Illustrative examples:

Attention is drawn to the following places, which may be of interest for search:

Portable telephones flexible display |

This place does not cover:

Arrangements to protect the display from incident light, e.g. hoods | |

Arrangements to support accessories mechanically attached to the display housing | |

Enclosure details of non-portable computers | |

Cooling arrangements for portable computers |

Attention is drawn to the following places, which may be of interest for search:

Protective covers or auxiliary enclosures for portable computers | |

Protective covers or auxiliary enclosures for portable telephones | |

Portable telephones with mechanically detachable modules |

This place does not cover:

Internal mounting structures of non portable computers |

Attention is drawn to the following places, which may be of interest for search:

Details of stand alone keyboards | |

Constructional details of keyboard switches | |

Portable telephones keypads |

Attention is drawn to the following places, which may be of interest for search:

Digitisers | |

Interaction with virtual keyboards displayed on a touch sensitive surface |

Attention is drawn to the following places, which may be of interest for search:

Movement typologies | |

Relative motion of the body parts to change the operational status of the portable telephone |

Attention is drawn to the following places, which may be of interest for search:

Portable telephones open/close detection |

This place does not cover:

Hinge details related to the transmission of signals or power |

Attention is drawn to the following places, which may be of interest for search:

Hinges for doors, windows or wings | |

Portable telephones hinge details |

This place covers:

Also optical transmission of data or inductive transmission of power between housings.

Attention is drawn to the following places, which may be of interest for search:

Camera details of portable telephones |

This place does not cover:

Touchscreens | |

Constructional details of pointing devices |

Attention is drawn to the following places, which may be of interest for search:

Joysticks in general | |

Constructional details of pointing devices in portable telephones |

This place covers:

Secondary touchscreens which are used only as input device (touchpad, virtual input devices), and not for information display.

Attention is drawn to the following places, which may be of interest for search:

Gestural input | |

Motion sensing in space for computer input |

This place covers:

Scanners for e.g. A4 sheets.

This place does not cover:

Barcode readers |

Attention is drawn to the following places, which may be of interest for search:

Scanners | |

Printers |

This place does not cover:

details of antennas disposed inside a computer | |

Interaction of portable devices with video on demand or television systems |

Attention is drawn to the following places, which may be of interest for search:

Aerials | |

Cordless telephones |

This place covers:

Cases and housing for computers and how computer components are "packed" , i.e. mounted within the housing . It also covers arrangements, e.g. cabling, to distribute the power generated by the power supply unit to the other computer components mounted within the casing.

This place covers:

Enclosures for computers, including constructional details of front or bezel.

This place does not cover:

Enclosures for portable computers |

Attention is drawn to the following places, which may be of interest for search:

Enclosures for electrical apparatuses in general |

This place covers:

Enclosures for non-standard computers, e.g. industrial computers, computers specifically adapted to special environments.

Attention is drawn to the following places, which may be of interest for search:

Shielding against electromagnetic interference in general |

This place covers:

Mounting structures for securing and/or interconnecting among them internal components within the enclosure of a computer system.

Attention is drawn to the following places, which may be of interest for search:

Mechanical coupling between device and bus | |

Mounting structures for printed circuits in general |

Attention is drawn to the following places, which may be of interest for search:

Housings for circuits carrying a CPU and adapted to receive expansion cards |

Attention is drawn to the following places, which may be of interest for search:

Mounting of expansion boards in general |

Used for the securing of expansion cards completely within the enclosure, and not to the connection to openings in the enclosure.

Attention is drawn to the following places, which may be of interest for search:

Securing of expansion boards in general |

Used for to the connection of expansion boards to openings in the enclosure so that at least a portion, or connector, of the expansion board is accessible from outside the enclosure.

Attention is drawn to the following places, which may be of interest for search:

Constructional details of disk drives housings in general |

Used for both optical drives and hard disk drives.

Attention is drawn to the following places, which may be of interest for search:

Power supply for computers |

This groups refers also to documents wherein the thermal management is achieved by lowering power consumption in order to reduce heat generation..

Documents also disclosing costructional details about the managed cooling arrangement should be also classified in G06F 1/20 if describing the cooling of a desktop computer or G06F 1/203 if describing the cooling of a portable computer.

Attention is drawn to the following places, which may be of interest for search:

Microprogramme loading | |

Restoration from data faults |

This place covers:

Power supplies for computers including:

- Power regulation;

- Power monitoring including means for acting in the event of power supply fluctuations or interruption;

- Power save.

This place does not cover:

Power supplies for memories |

Attention is drawn to the following places, which may be of interest for search:

Systems for regulating electric or magnetic variables |

This place covers:

Arrangements with switchable, multiple power supplies (typical example is AC and battery, but may also include multiple batteries, fuel cells or solar panels).

This place does not cover:

Means for acting in the event of power-supply failure or interruption, e.g. power-supply fluctuations |

This place covers:

Arrangements to supply power to external peripherals, either directly from the computer or under computer control (typical cases are the supply of power through a USB interface and the power strips).

This place covers:

Arrangements to monitor, and only monitoring, power supply parameters (e.g. voltage and/or current).

This place does not cover:

Means for acting in the event of power-supply failure or interruption, e.g. power-supply fluctuations |

This place does not cover:

For resetting only |

Attention is drawn to the following places, which may be of interest for search:

Involving the processing of data-words |

This place covers:

Means to save power in computers, including devices, methods and combinations of devices and method features.

This place covers:

Power saving obtained by switching, in relation to events of any type, between computing device operating modalities implying different power consumption levels. As opposed to power saving arrangements and/or methods of a permanent or continuous nature.

This place covers:

Power saving triggered by a certain event and/or condition detected by monitoring or supervision of e.g. hardware, communication, processing tasks.

Used when the peripheral monitored does not belong to any of the subgroups: G06F 1/3218, G06F 1/3221 or G06F 1/3225.

This place covers:

Power saving initiated when a task completion is detected (typical cases are the completion of processing tasks, e.g. programs, applications, routines).

This place covers:

Power saving initiated when the user absence/presence is detected, e.g. through a camera and/or sensors.

This group is not to be used when the user absence/presence is inferred by a user inactivity period, e.g. absence of keyboard input. Subgroups referring to monitoring of peripheral devices to be used in such cases, i.e. G06F 1/3215 and subgroups.

This place covers:

Power saving obtained by selectively reducing power consumption of all or individual components of a computing system. Such reduction can be achieved in different ways, e.g. by lowering the clock frequency, by stopping the supply of the clock signal, by lowering the voltage, by stopping the supply of power, by task scheduling.

This place covers:

Power saving by stopping clock generation or distribution to a computer or a component.

This place covers:

Power saving taking place in the processing unit of the computer, intended as central processing unit (CPU), microcontroller unit (MCU), microprocessor.

This place covers:

Power saving in optical (or magneto-optical) disk drives, e.g. CD, DVD, Blue-Ray, etc.

This place does not cover:

Power saving in storage systems (e.g. not in disk drives within a computer system) |

This place covers:

Power saving by selectively reducing power consumption of individual components of a computer system. Such reduction can be achieved in different ways, e.g. by lowering the clock frequency or stopping the clock, by lowering the voltage, by stopping the power supply (power gating).

Attention is drawn to the following places, which may be of interest for search:

This place covers:

Includes inter alia arrangements in which a barcode reader is used to input data to a computer and in particular drivers for barcode or QR code readers.

Recognition of data; presentation of data; record carriers; handling record carriers: G06K.

This place does not cover:

Specific input/output arrangements | |

Other optical apparatus |

Attention is drawn to the following places, which may be of interest for search:

Viewers photographic printing | |

Electrography, magnetography | |

Constructional details of barcode readers | |

Reading of RFID record carriers | |

Constructional details of RFID record carriers | |

Use of barcode readers or RFIDs in data processing systems for business applications | |

Wireless phone using NFC or a two-way short-range wireless interface | |

Facsimile per se |

In this place, the following terms or expressions are used with the meaning indicated:

TUI | a user interface in which a person interacts with digital information through a physical environment, i.e. by manipulating physical objects (e.g. in the same way as moving pieces of a game on a tablet), often using RFID or NFC. |

In patent documents, the following abbreviations are often used:

TUI | Tangible User Interface |

RFID | Radio-Frequency Identification |

NFC | Near Field Communication |

This place covers:

Specific arrangements for input through a video camera, not covered by G06F 3/01 - G06F 3/16, e.g. details of the interface linking the camera to the computer.

This group was originally meant for devices adapting analog video cameras to computer entry.

Attention is drawn to the following places, which may be of interest for search:

Tracking user body for computer input | |

Pointing device integrating a camera for tracking its own position with respect to an imaged reference surface or the surroundings | |

Tracking a projected light spot generated by a light pen or a "laser pointer" indicating a position on a display surface | |

Digitisers using a camera for tracking the position of objects with respect to an imaged reference surface | |

Recognising movements or behaviour, e.g. recognition of gestures, dynamic facial expressions; Lip-reading | |

Television cameras |

Attention is drawn to the following places, which may be of interest for search:

Digital input from, or digital output to, record carriers | |

Digital stores in which the information is moved stepwise using magnetic elements and thin films in plane structure | |

Digital stores in which the information is moved stepwise using semiconductor elements | |

Organisation of a multiplicity of shift registers |

Old technology, not used anymore.

This place covers:

Input arrangements, or combined input and output arrangements, for interaction between user and computer.

Particularly, said input arrangements include those based on the interaction with the human body, e.g.

- gloves for hand or finger tracking;

- eye or head trackers;

- devices using bioelectric signals, e.g. detecting nervous activity;

- arrangements for providing computer generated force feedback in input devices.

This place does not cover:

Sound input, sound output including multimode user input, i.e. combining audio input (e.g. voice input) with other user input |

Attention is drawn to the following places, which may be of interest for search:

Interaction techniques based on graphical user interfaces [GUI] |

Diagnosis; surgery; identification: A61B

Recognition of data; presentation of data; record carriers; handling record carriers: G06K

This place does not cover:

Blind teaching |

Attention is drawn to the following places, which may be of interest for search:

Measuring of parameters or motion of the human body or parts thereof for diagnostic purposes | |

For handicapped people in general | |

Games using an electronically generated display and player-operated input means | |

Robot control | |

Stereoscopic optical systems | |

Recognising human body or animal bodies | |

Acquiring or recognising human faces, facial parts, facial sketches, facial expressions | |

Tactile signalling | |

Virtual reality arrangements for interacting with music, including those with tactile feedback | |

For electrophonic musical instruments | |

Electronic switches characterised by the way in which the control signals are generated |

This place covers:

For the scope of this group, Head-tracking is interpreted as covering face detection and tracking.

Attention is drawn to the following places, which may be of interest for search:

Head-tracking for image generation in head-mounted display | |

Use of head-tracking for image generation | |

3D image generation in augmented reality | |

Using viewer tracking |

In patent documents, the following abbreviations are often used:

HMD | Head-Mounted Display |

This place does not cover:

Input arrangements based on nervous system activity detection |

Attention is drawn to the following places, which may be of interest for search:

Apparatus for testing the eyes and instruments for examining the eyes | |

Instruments for determining or recording eye movement | |

Acquiring or recognising eyes |

In patent documents, the following words/expressions are often used as synonyms:

- "eye tracking" and "gaze tracking"

This place covers:

Also covers hand-worn keyboards

Manipulators; chambers provided with manipulation devices: B25J

Attention is drawn to the following places, which may be of interest for search:

Finger worn arrangements for converting the position or the displacement of a member into a coded form |

In this place, the following terms or expressions are used with the meaning indicated:

Data glove (sometimes called a "wired glove" or "cyberglove") | an input device for human–computer interaction worn like a glove |

Attention is drawn to the following places, which may be of interest for search:

Detecting bioelectric signals for diagnostic purpose | |

Bioelectrical control, e.g. myoelectric |

This place covers:

Dynamic force or tactile feedback arrangements. Also passive feedback arrangements but only if they are dynamically reconfigurable under computer control, e.g. buttons raised from a touchpad surface using electronic muscle or similar.

- Manipulators; chambers provided with manipulation devices: B25J

- Conjoint control of vehicle sub-units of different type or different function; control systems specially adapted for hybrid vehicles; road vehicle drive control systems for purposes not related to the control of a particular sub-unit: B60W

- Systems acting by means of fluids; fluid-pressure actuators, e.g. servo-motors: F15B

- Control or regulating systems in general: G05B

- Mechanical control devices: G05G

Attention is drawn to the following places, which may be of interest for search:

Passive (and non reconfigurable) feedback arrangements on a touchscreen, e.g. overlays with reliefs for indicating keys of a virtual keyboard | |

Hand grip control means for manipulators | |

Tactile feedback for vehicle driver | |

Servo-motor systems giving the operating person a "feeling" of the response of the actuated device | |

Means for enhancing the operator's awareness of arrival of the controlling member (knob, handle) at a command or datum position; Providing feel, e.g. means for creating a counterforce | |

Tactile presentation of information, e.g. Braille display | |

Keyboards characterised by tactile feedback features | |

Piezoelectric actuators |

This place covers:

Gesture interaction as a sequence and/ or a combination of user movements captured using various sensing techniques such as (among others) cameras monitoring the user, arrangements for interaction with the human body, input by means of a device moved freely in 3D space or opto-electronic detection arrangements.

This place does not cover:

Gestures made on the surface of a digitiser and/or in close proximity to this surface for digitisers capable of touchless position sensing and/or measuring also the distance in the Z direction |

Attention is drawn to the following places, which may be of interest for search:

Arrangements for interaction with the human body | |

Detection arrangements using opto-electronic means | |

Input by means of (pointing) device or object moved freely in 3D space | |

Acquiring or recognising (static) human faces, facial parts, facial sketches, facial expressions | |

Recognising movements or behaviour, e.g. recognition of gestures, dynamic facial expressions; Lip-reading | |

Lip-reading assisted speech recognition |

Handling natural language data: G06F 40/00

Attention is drawn to the following places, which may be of interest for search:

Inputting characters | |

Handling non-Latin characters, e.g. kana-to-kanji conversion | |

Processing of non-Latin text |

This place covers:

Input arrangements using manually operated switches, e.g. using keyboards or dials, insofar as they are stand-alone devices or integrated in a fixed computer system. Includes wired or wireless keyboards which are not mechanically linked to a portable computer.

Attention is drawn to the following places, which may be of interest for search:

Details related to integrated keyboard of portable computers | |

Keyboard switches per se | |

Electronic switches characterised by the way in which the control signals are generated |

Attention is drawn to the following places, which may be of interest for search:

Special layout of keys | |

Palm(wrist)-rests not integrated in the keyboard | |

Wrist worn wrist rests | |

Document holders for typewriters | |

Input/Output devices for watches | |

Details of keys/push buttons | |

Switches having rectilinearly-movable operating part or parts | |

Constructional details of keyboards having such switches | |

Electronic switching or gating i.e. not by contact-making or -braking | |

Proximity switches | |

Touch switches with electronic switching | |

Capacitive touch switches | |

Force resistance transducer | |

Optical touch switches | |

Piezoelectric touch switches | |

Resistive touch switches | |

Keyboard, i.e. having a plurality of control members, with electronic switching | |

With optoelectronic devices | |

With magnetic movable elements | |

With capacitive movable elements |

In patent documents, the following abbreviations are often used:

RSI | Repetitive Stress Injuries |

Attention is drawn to the following places, which may be of interest for search:

Integration of a mini joystick in a portable computer | |

Integration of a mini joystick in a keyboard | |

Details of the interface with a computer | |

Joysticks with a pivotable rigid stick |

This place does not cover:

Adjusting the tilt angle of the integrated keyboard in a mobile computer |

Attention is drawn to the following places, which may be of interest for search:

Constructional details of barcode readers |

This place does not cover:

Integration of a mini joystick in a portable computer | |

Constructional details of pointing devices | |

Joysticks with a pivotable rigid stick |

This place does not cover:

For keyboards integrated in a laptop computer |

This place covers:

Any keyboard designed or modified to control a specific software application or specific hardware, e.g. by integrating dedicated keys. Key layouts in alternative to the QWERTY standard are also classified in this group.

Attention is drawn to the following places, which may be of interest for search:

Devices for teaching typing |

This place does not cover:

Arrangements for reducing the size of the integrated keyboard in a portable computer | |

Arrangements for ergonomically adjusting the disposition of keys of a keyboard |

Attention is drawn to the following places, which may be of interest for search:

Document holders for typewriters |

This place covers:

Input arrangements using manually operated switches, e.g. using keyboards or dials, further comprising cooperation and interconnection of the input arrangement with other functional units of a computer.

This place does not cover:

Arrangements for converting discrete items of information into a coded form. Arrangements for converting the position or the displacement of a member into a coded form |

Attention is drawn to the following places, which may be of interest for search:

Keyboards integrating additional peripherals | |

Arrangements for converting the position or the displacement of a member into a coded form |

This place covers:

Keyboard interfaces and drivers; peripherals emulating a keyboard (e.g. producing "keystroke input" signals); devices providing additional buttons or foot operated switches and connected between keyboard and PC.

Also comprises KVM switches.

Attention is drawn to the following places, which may be of interest for search:

Virtual keyboards displayed on a touchscreen | |

Coding in connection with keyboards, i.e. coding of the position of operated keys |

In this place, the following terms or expressions are used with the meaning indicated:

KVM | a KVM switch allows a user to control one or multiple computer(s) from one or multiple KVM device(s) |

In patent documents, the following abbreviations are often used:

KVM | Keyboard, Video, Mouse |

This place covers:

Constructional details related to the wireless link, e.g. position of the IR transmitter/receiver as well as protocol details for the wireless transmission of keyboard codes.

Attention is drawn to the following places, which may be of interest for search:

Means for saving power, monitoring of peripheral devices | |

Information transfer between I/O devices and CPU, e.g. on bus |

In this place, the following terms or expressions are used with the meaning indicated:

Cordless keyboards | wireless keyboards; they are also often called according to the technology used: infrared keyboard, radio keyboard, WLAN keyboard, Bluetooth® keyboard |

This place covers:

Character input using a reduced number of keys, e.g. with respect to the alphabet, i.e. multivalued keys. Covers character input methods wherein a character is entered by tracing it on a matrix of switches (keys). Covers character input methods where a character is entered as a sequence of strokes on different keys or on a same key.

Attention is drawn to the following places, which may be of interest for search:

Interaction with virtual keyboards displayed on a touchscreen |

This place covers:

Keyboards or keypads having keys that can be operated not only vertically but also laterally to actuated separate switches associated to different key codes.

Attention is drawn to the following places, which may be of interest for search:

Character input using (e.g. 2 or 4 or 8) directional cursor keys for selecting characters in cooperation with displayed information |

This place covers:

Chord keyboards even if they are split in two or more parts, i.e. the predominant feature is the fact that chording is required to enter a character.

This place does not cover:

Character input using switches operable in different directions |

In this place, the following terms or expressions are used with the meaning indicated:

Chord | only an almost simultaneous depression of several keys |

Attention is drawn to the following places, which may be of interest for search:

Selecting from displayed items by using keys for other purposes than character input |

This place covers:

Character input using retrieval techniques from a database or dictionary based on previously inputted characters, e.g. for predicting and proposing word completion alternatives.

Covers inter alia T9, iTap and similar techniques.

Attention is drawn to the following places, which may be of interest for search:

Converting codes to words or guess-ahead of partial word inputs |

In this place, the following terms or expressions are used with the meaning indicated:

T9 (stands for Text on 9 keys) | a predictive text input technology for mobile phones, developed by Tegic Communications |

iTap | a predictive text technology for mobile phones, developed by Motorola |

This place covers:

Any keyboard in which the function assigned to all or some of the keys can be reprogrammed, e.g. changing alphabetical keys according to language, programming dedicated function keys.

This place does not cover:

Key guide holders |

Attention is drawn to the following places, which may be of interest for search:

Virtual keyboards on a touchscreen | |

Scrambling keyboard with display keys in electronically operated locks | |

Scrambling keyboard in electronically banking systems (POS,ATM) | |

Display on the key tops of musical instruments: | |

Switches with programmable display | |

Display on the key tops in general | |

Telephone set with programmable function keys |

Attention is drawn to the following places, which may be of interest for search:

Display of decimal point | |

Complete desk- top or hand- held calculators |

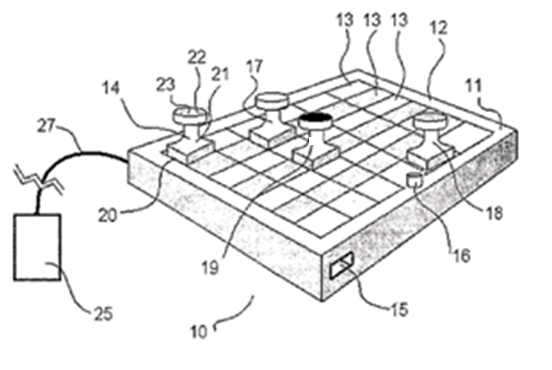

This place covers:

This group is used only for "exotic" input devices corresponding to the wording of the definition and not fitting in any of the subgroups, for example arrangements detecting the position or the displacement of tangible user interfaces comprising RFIDs tags or bar codes interacting with a surface (such as chessboard-like surface) where the position detection technique is not covered by any of the subgroups of G06F 3/03.

Example:

Attention is drawn to the following places, which may be of interest for search:

Interaction with a tangible user interface other than detecting its location or displacement | |

Electronic game devices per se | |

Coordinate identification of nuclear particle tracks | |

Telemetry of coordinates |

In this place, the following terms or expressions are used with the meaning indicated:

A Tangible User Interface (TUI) | a user interface in which a person interacts with digital information through a physical environment, i.e. by manipulating physical objects (e.g. in the same way as moving pieces of a game on a tablet), often using RFID or NFC |

In patent documents, the following abbreviations are often used:

TUI | Tangible User Interface |

RFID | Radio-Frequency IDentification |

NFC | Near Field Communication |

If the moving part is the sensor then the subject-matter belongs to G06F 3/0304, if the observed target (e.g. finger) is moving then the subject-matter belongs to G06F 3/042.

This place does not cover:

Constructional details of pointing devices not related to the detection arrangement using opto-electronic means | |

Digitisers using opto-electronic means |

Attention is drawn to the following places, which may be of interest for search:

Systems where the position detection is based on the raster scan of a cathode-ray tube (CRT) with a light pen | |

Measuring arrangements characterised by the use of optical means | |

Optical encoders | |

Position fixing using optical waves | |

Prospecting or detecting by optical means | |

Static switches using electro-optical elements in general | |

Optical switches | |

Optical touch switches |

Attention is drawn to the following places, which may be of interest for search:

Thumb wheel switches |

This place covers:

Tracking relative movement in co-operation with a regularly or irregularly patterned surface, e.g. arrangements for detecting relative movement of an optical mouse with respect to a generic surface optically detected as irregularly patterned (table, desk top, ordinary mouse pad) or with respect to a surface (e.g. mouse pad) encoded with an optically detectable regular pattern.

Arrangements for detecting absolute position of a member with respect to a regularly patterned surface, e.g. pen optically detecting position-indicative tags printed on a paper sheet.

This place does not cover:

Digitisers characterised by the transducing means |

Attention is drawn to the following places, which may be of interest for search:

Details of optical sensing in input devices | |

Arrangement for interfacing a joystick to a computer | |

Constructional details of joysticks |

For finger worn pointing devices covered by this group and its subgroups add the Indexing Code G06F 2203/0331.

In patent documents, the following abbreviations are often used:

RSI | Repetitive Stress Injury |

Attention is drawn to the following places, which may be of interest for search:

Integration of a mini joystick in a portable computer | |

Integration of a mini joystick in a keyboard | |

Sliders, in which the moving part moves in a plane | |

Details of the interface with a computer | |

Joysticks with a pivotable rigid stick | |

Switches with generally flat operating part depressible at different locations |

This place covers:

Devices sensing their own position or orientation in a three dimensional space, allowing thereby the user to input up to 6 coordinates (position + orientation) by moving the device. Covers inter alia 3D mice.

Remote control based on movements G08C.

Attention is drawn to the following places, which may be of interest for search:

3D input gestures | |

Input devices using opto-electronic sensing |

This place covers:

Pens detecting the presence of light on one point (such as a CRT scanning beam).

Light emitting pens positioned in contact or proximity of the pointed position.

Attention is drawn to the following places, which may be of interest for search:

Pens comprising an optical sensor for 1 or 2 dimensional position detection | |

Light emitting pointers per se used for marking with a light spot the pointed position from a distance |

This place does not cover:

Mouse/trackball convertible-type devices, in which the same ball is used to track the 2-dimensional relative movement |

Specific Indexing Codes G06F 2203/0332 - G06F 2203/0337 are associated to this group for some constructional details.

This place covers:

Pens other than optically sensing pens or light pens (e.g. for use in combination with a digitiser). Constructional details of pens in general irrespectively of the interaction technology.

Pens used for handwriting recognition:G06V 30/1423, G06V 10/12.

This place does not cover:

Details of optically sensing pens | |

Light pens |

This place covers:

Touch surface for sensing the relative motion of a finger over the surface.

Attention is drawn to the following places, which may be of interest for search:

Digitisers |

Specific Indexing Codes G06F 2203/0338 and G06F 2203/0339 are associated to this group for some constructional details.

This place does not cover:

Mouse/trackball convertible-type devices, in which the same ball is used to track the 2-dimensional relative movement |

Attention is drawn to the following places, which may be of interest for search:

Input arrangements for vehicle instruments | |

Incremental encoders | |

Sliding switches | |

Rotary encoding wheels -"thumb-wheel switches" |

Attention is drawn to the following places, which may be of interest for search:

Control circuits or drivers for touchscreens or digitisers | |

Graphical user interfaces (GUI) in general | |

Pointing device drivers modified to control cursor appearance or behaviour taking into account the presence of displayed objects |

This place covers:

Tracking a projected light spot generated by a light pen or a "laser pointer" indicating a position on a display surface, drivers for light pen systems.

Attention is drawn to the following places, which may be of interest for search:

Light emitting pointers per se used for marking with a light spot the pointed position from a distance | |

Light emitting pens positioned in contact or proximity of the pointed position | |

Light pen using the raster scan of a CRT |

Attention is drawn to the following places, which may be of interest for search:

Furniture aspects | |

Platforms for supporting wrists as table extension |

This place covers:

For example:

This place covers:

Position sensing of movable objects such as fingers or pens in contact with a surface or within a relative small distance to this surface (hovering).

Attention is drawn to the following places, which may be of interest for search:

Touchscreens integrated in a portable computer | |

Integration of touchpad in a portable computer (laptop, PDA) | |

3D input gestures | |

Integration of touchpad in a keyboard | |

True 3D computer input devices with a freely movable member | |

Pens for interaction between user and computer | |

Constructional details of touchpads | |

Accessories for pointing devices | |

Touch interaction within a graphical user interface [GUI] |

In this area, Indexing Codes G06F 2203/04101 - G06F 2203/04114 dealing with details which may be related to different sensing technologies are used in parallel to the classification scheme.

Subgroups G06F 3/0412 and G06F 3/0416 -G06F 3/04186 are not explicit to a specific sensing technology but describe details about the integration within a display or the driving/interface of the digitiser.

For documents belonging to these subgroups, if further relevant details related to the sensing technology are disclosed, the corresponding subgroup of G06F 3/041 that is best related to the sensing technology employed should be doubly allocated as invention information.

If the sensing technology is indicated only with minor details, the sensing technology (if any) should be indicated as additional information.

In this place, the following terms or expressions are used with the meaning indicated:

Surface | either as a physical surface or as a virtual one, such as a virtual interaction plane floating in the air |

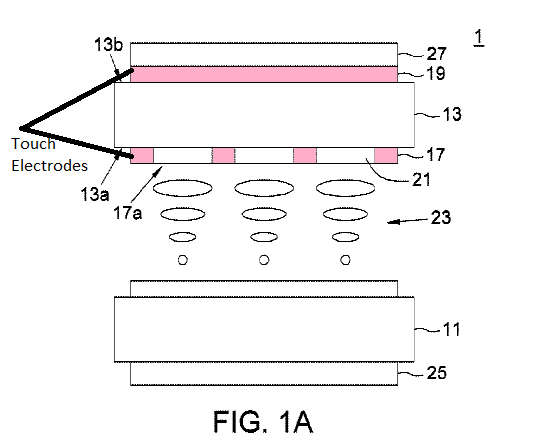

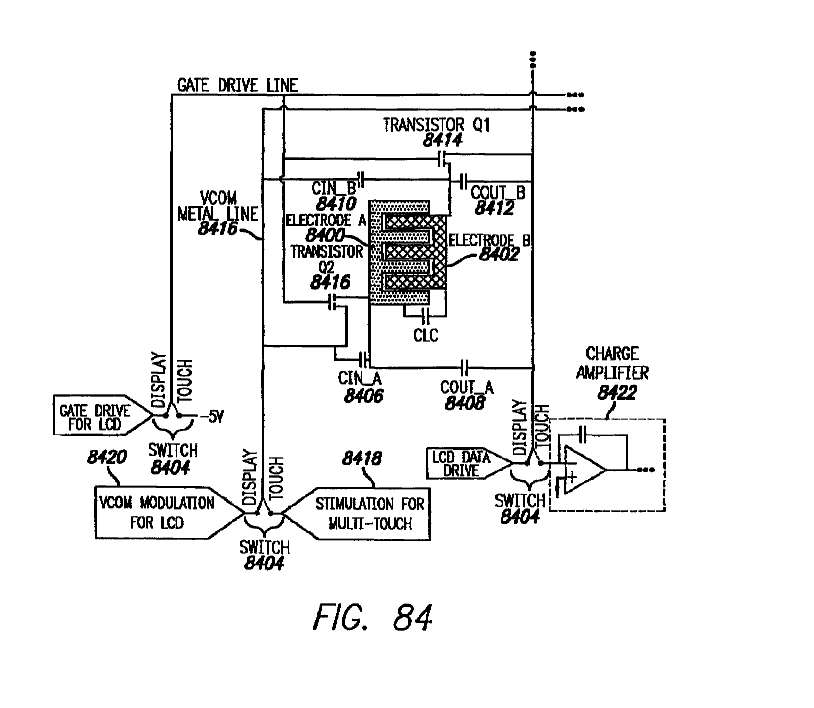

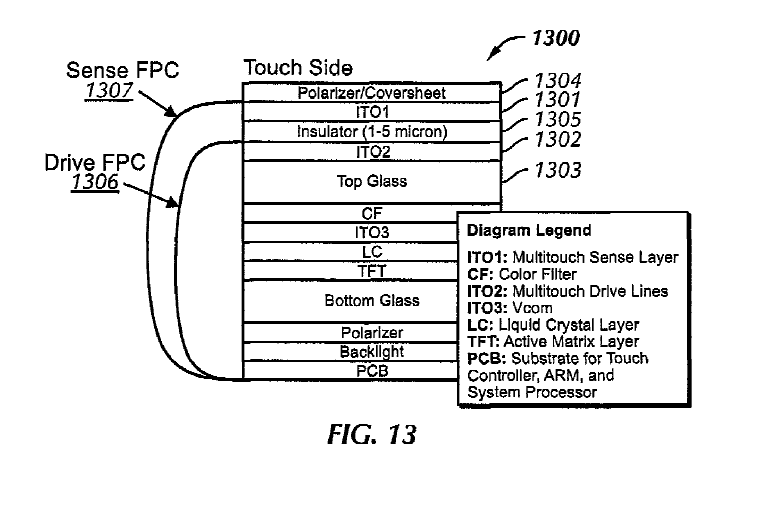

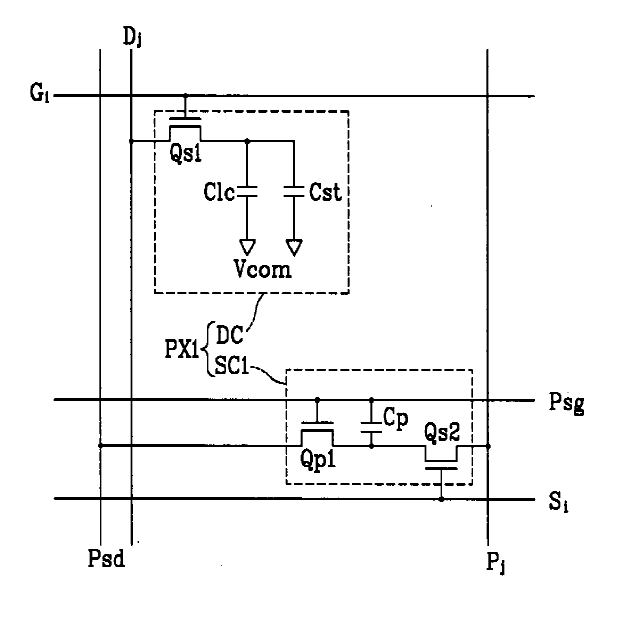

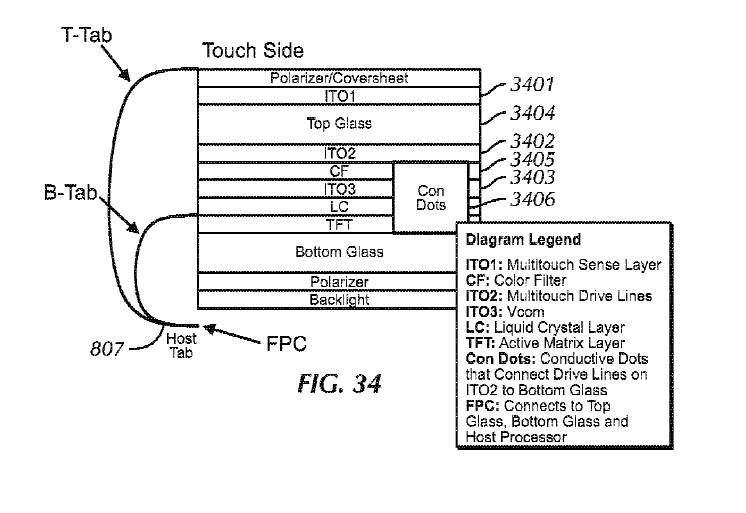

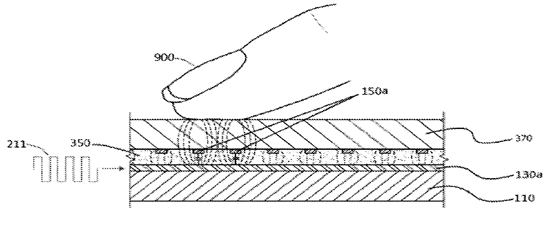

This place covers:

Structural details and methods of driving a combination of displays with digitisers that share at least one constitutive part of both the touch sensing technology as well as the display technology (e.g. a common electrode for LCD control and a touch electrode (i.e. driving or sensing) for capacitive touch sensing, a common electrode being used as a guard/shield electrode in touch sensing, or a common electrode that is specifically floated during a touch driving/sensing period).

Examples:

Structural details and methods of driving a display and a digitizer in which the digitizer is either wholly or in part within the structural confines that make up the display panel of the display device (e.g., a sensor pixel that is adjacent to the display pixel) or the sensor is arranged to utilize at least one structural component of the display panel (e.g. such as the top substrate of the display pane).

Examples:

Attention is drawn to the following places, which may be of interest for search:

Constructional details of LCDs | |

Driving details of LED/OLED | |

Driving details of LCDs | |

Construction details of OLED displays |

Documents disclosing both a specific display panel (LCD, OLED etc.) and touch sensing are doubly classified in the relevant areas (for example: G02F for LCD, H10K for OLEDs, and G09G for methods of driving displays), pertaining to the respective types of display panels as well as in G06F 3/0412.

Devices in which a component is shared between touch detection circuitry and display driving circuitry, for example, a shared electrode for touch detection and display driving wherein the details of both the touch detection and the display driving are disclosed should be classified in the relevant areas either G09G (depending upon the type of display device) as well as in G06F 3/0412.

Devices in which construction details of both LCD panel and touch components are disclosed, but touch detection is only nominally disclosed should be classified only in G02F 1/13338 and only classified in G06F 3/0412 as an Additional.

Construction details of OLED display components integrated with touch detection components wherein the disclosure primarily concerns the OLED and minimally recites touch circuitry is classified in H10K 59/40 and only classified in G06F 3/0412 as an Additional.

This place covers:

Touch position determined by the analysis of the signals provided by pressure/force sensors.

Measuring force or stress in general: G01L 1/00.

Attention is drawn to the following places, which may be of interest for search:

Pressure sensors for measuring the pressure or force exerted on the touch surface without providing the touch position | |

Tactile force sensors | |

Force resistance touch switches | |

Piezoelectric touch switches |

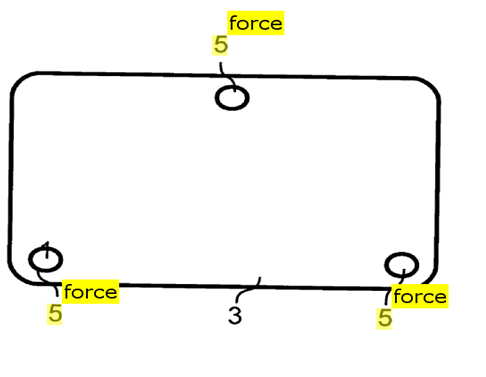

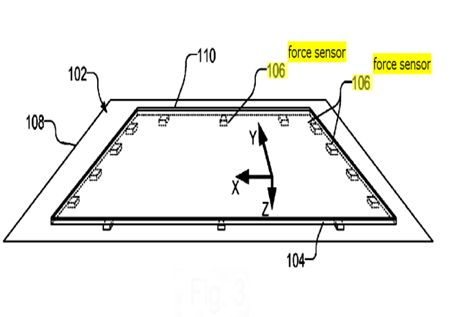

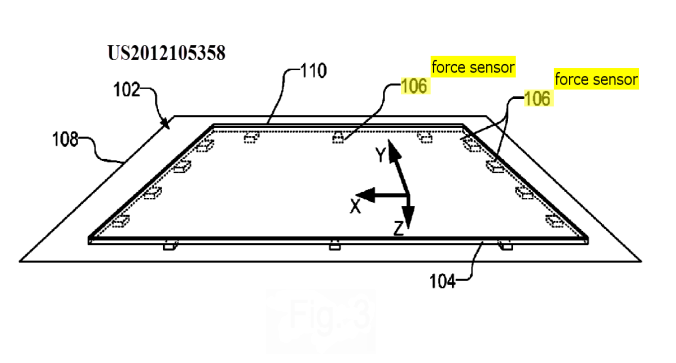

This place covers:

Touch position determined by the analysis of the signals provided by a plurality (reduced number) of discrete pressure/force sensors disposed at several points of (e.g. under) the touch sensing surface, e.g. at the corners or the side of a touch sensing plate.

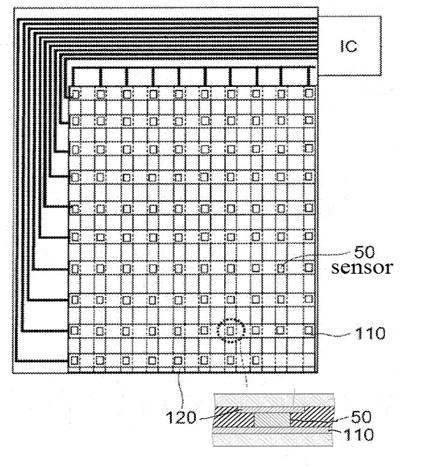

This place covers:

Touch position determined by the analysis of the signals provided by either virtual pressure sensors generated by intersection nodes of a grid of sensing lines interacting with a pressure sensitive medium or an array of discrete pressure/force sensors delivering a variable (not a single Boolean 0/1) signal, the array extending over the whole area of the touch sensing surface, e.g. a grid of sensors disposed under the touch sensing surface.

This place does not cover:

Position sensing using the local deformation of sensor cells |

This place covers:

Digitisers having a grid of crossing wires brought into virtual contact when pressure is exerted on the interaction surface, the virtual contact is established through a pressure sensitive layer disposed between the wire layers and made of a material that resistance diminishes under an applied pressure used to provide a "binary" output. The touch position is determined only by the contacting wires (scanning line and column) and not by the analog value of the sensed signal.

Attention is drawn to the following places, which may be of interest for search:

Tactile force sensors | |

Force resistance touch switches | |

Piezoelectric touch switches |

Attention is drawn to the following places, which may be of interest for search:

Touch interaction with a GUI |

This place covers:

Digitiser control allowing exchange of data with external devices via the digitiser sensing hardware (touch sensing electrodes, touch sensing coils, etc...), including exchange of information with smart pens as long as it concerns data transmission via the touch detection hardware.

Not for transmission of data between devices using only transmission paths other than the touch sensing hardware (e.g. wired or wireless network).

Attention is drawn to the following places, which may be of interest for search:

Remote control transmission over wireless link | |

Near-field transmission systems | |

Data switching networks | |

Mobile phones interface using two way short range wireless interface |

This place covers:

Routing between sensing electrodes and controller or connector, details on wiring and connectors.

This place covers:

For example grouping electrodes for changing the detection speed, resolution or sensitivity (including proximity distance), detection of multiple touches, detection of both pen and finger or, combination of multiple touch technologies.

This place does not cover:

Synchronisation with the driving of the display or the backlighting unit to avoid interferences generated internally |

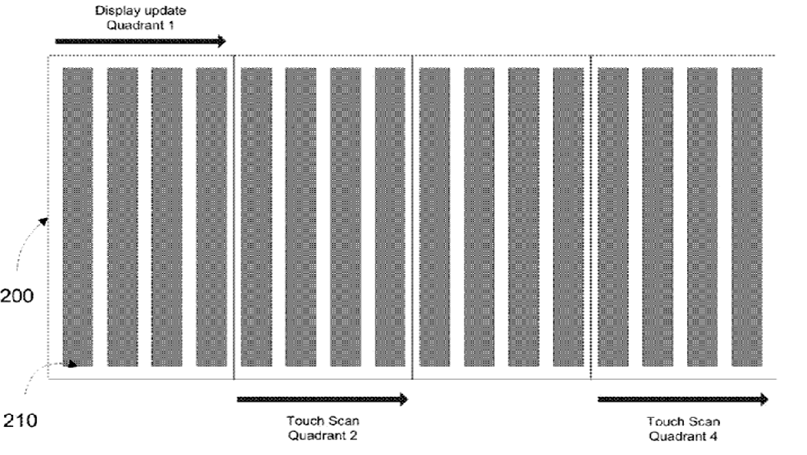

This place covers:

Synchronisation of the touch detection signals with the display (or backlight) driving signals whenever the digitiser is integrated in the display or not.

This place covers:

Correcting or resolving an ambiguous detected touch, resulting from either

- an ambiguous touch location measured by the digitiser (e.g. correcting a detected large single touch into more than one smaller and adjacent touches, a partial touch at an edge of a digitiser into a full touch, a detected touch with an unwanted detected event like hover/palm rejection, cracks, water droplets, impurities, ghost touches, or gravity center due to tilt/angle of the input device) or

- an ambiguous interaction with a GUI on a touch screen, wherein the touch location as measured by the digitiser is unambiguous (e.g. correcting a detected touch to a user intended touch position)

Documents disclosing disambiguation of an interaction with a GUI on a touch screen, wherein the touch location as measured by the digitiser is unambiguous, should be doubly classified in G06F 3/0488 and below.

Optical scanners: G06K 7/10544.

Attention is drawn to the following places, which may be of interest for search:

Pens detecting optically their absolute position with respect to a coded surface | |

Systems where the position detection is based on the screen scanning with a light pen | |

Measuring arrangements characterised by the use of optical means | |

Optical encoders | |

Position fixing using optical waves | |

Prospecting or detecting by optical means | |

Static switches using electro-optical elements in general | |

Optical switches | |

Optical touch switches |

When there is a doubt whether the subject matter belongs to G06F 3/0304 and below or to G06F 3/042 and below, the rule of thumb is: if the moving part is the sensor then it belongs to G06F 3/0304 and below, if the observed target (e.g. finger) is moving then it belongs to G06F 3/042 and below. In any case, the subclasses G06F 3/042 and below are used only in the context of interaction with a surface as defined in G06F 3/041 or in close proximity of this surface; they are not used in the context of a true 3D interactive environment.

In patent documents, the following abbreviations are often used:

FTIR | Frustrated Total Internal Reflection |

In this place, the following terms or expressions are used with the meaning indicated:

Beam | a narrow beam emitted in a given direction, not as a bright band of light or as an omnidirectional lightening; in the context of beams propagating from one side towards receivers on the opposite side in a grid like arrangement, the beam may have a triangular (or conical) shape with a slightly broader opening angle in order to be sensed by several receivers on the opposite side but not covering the whole array of receivers. |

Attention is drawn to the following places, which may be of interest for search:

Details of moving scanning beam in optical scanners |

This place covers:

Also documents where the acoustic wave is produced by knocking or rubbing the movable member (finger or pen) on the touch surface without any other vibration generator.

Attention is drawn to the following places, which may be of interest for search:

In patent documents, the following abbreviations are often used:

SAW | Surface Acoustic Waves |

This place covers:

Position detection using pens able either to emit acoustic waves using a dedicated wave generator (e.g. piezoelectric or mechanical vibrators, ultrasound generators or sparks) or to sense the propagating waves arriving through the surface.

Attention is drawn to the following places, which may be of interest for search:

Documents where the movable member (finger or pen) generates the waves but has no acoustic source | |

Piezoelectric vibrators |

This place covers:

Passive movable member (finger or pen) disturbing the propagating waves within the substrate.

Attention is drawn to the following places, which may be of interest for search:

Means for converting the output of a sensing member to another variable by varying capacitance | |

Capacitive proximity switches | |

Capacitive touch switches |

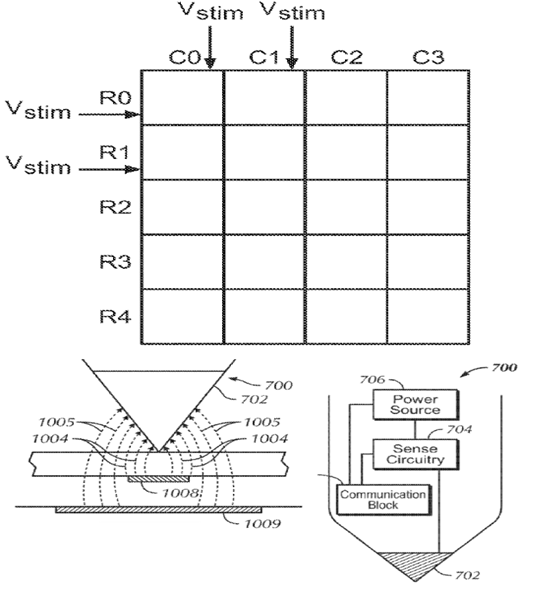

This place covers:

Digitisers using the capacitive coupling between the edge of a pointing pen or a similar sensing device and touch sensing conductors (electrodes) of the position sensing surface wherein the pen detects changes in electric potential of the conductors generated by the tablet (e.g. tablet driving signals); corresponding to JP FI: G06F 3/044.

Attention is drawn to the following places, which may be of interest for search:

Transmission of data between devices using the touch sensing hardware as transmission path |

This place covers:

Digitisers using the capacitive coupling between the edge of a pointing pen or a similar input device and touch sensing conductors (electrodes) of the position sensing surface wherein active pens generate changes in electric potential of tablets, corresponding to JP FI: G06F 3/044.

Attention is drawn to the following places, which may be of interest for search:

Transmission of data between devices using the touch sensing hardware as transmission path |

This place covers:

Digitisers using a single layer of sensing electrodes, i.e. sense and/or drive electrodes. The electrodes may be interconnected by bridges at crossings. The connecting bridge may be in another layer but all the sensing electrodes are in the same one.

This place covers:

Digitisers using a single layer of sensing electrode which is made of a single piece of conducting material extending on the detection area and covered by a dielectric material.

This place covers:

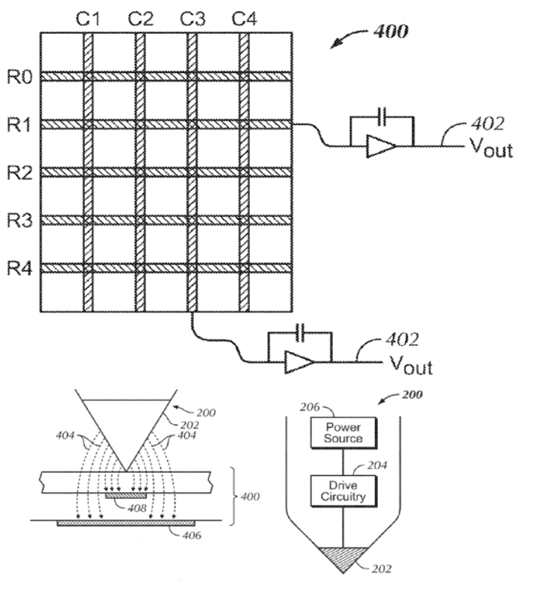

Digitisers using at least two layers of sensing electrodes, i.e. sense and/or drive electrodes, separated either by a solid dielectric layer or by a gap which could be filled by a dielectric material.

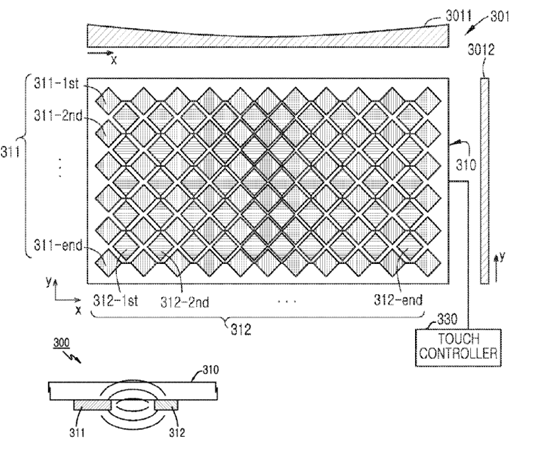

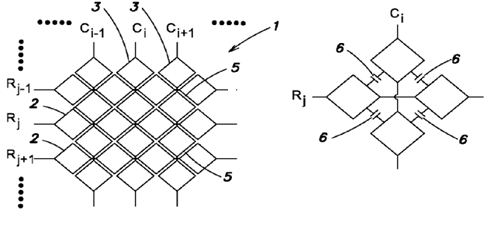

This place covers:

Digitisers comprising a plurality of sets of parallel sensing and/or driving electrodes extending in at least two crossing directions; each "row" or "column" electrode may be either a single piece electrode or a plurality of interconnected electrodes (e.g. via bridges over the electrodes in the crossing direction) making a virtual electrode extending along the given direction.

This place covers:

Digitisers comprising an array of cells, e.g. made by the crossing of "row" and "column" electrodes, which are deformed under the pressure of a touching object, inducing a change in their capacitance.

This place covers:

The electrodes have shapes optimised to obtain a specific effect, e.g. increasing fringe field, better resolution or avoiding moiré effect.

If the electrode design or pattern exhibits an irregular or non-conventional shape without mentioning any specific effect then this symbol should be allocated as additional information.

Attention is drawn to the following places, which may be of interest for search:

Touch switches |

Attention is drawn to the following places, which may be of interest for search:

Resistive potentiometers | |

Resistive touch switches |

Attention is drawn to the following places, which may be of interest for search:

Means for converting the output of a sensing member to another variable by varying inductance | |

Electromagnetic proximity switches using a magnetic detector |

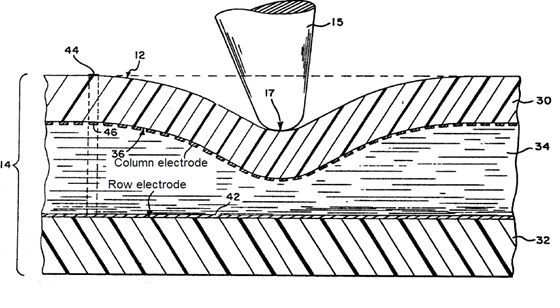

This place covers:

Digitisers having a grid of crossing wires brought into contact when pressure is exerted on the interaction surface. The contact may be a direct contact or through a pressure sensitive switch making a connection between the wires. It includes arrays of switches integrated in a display where a galvanic contact is established between rows and columns when the user presses the display surface.

When wires or switches are integrated in a display, G06F 3/0412 should also be used.

This place covers:

Subject matter where the focus is on the way the user can interact with the displayed data, usually by means of pointing devices, irrespective of the type of data treated by the software application or the type of device embedding data processing capability.

As to the design of an interaction technique, this is most commonly determined by one or more of three factors, also in combination:

- the specific behaviour or appearance, of the graphical element or virtual environment;

- the kind of input events that can be generated by a specific input device used to interact with the displayed elements of the GUI;

- the type of operation or function to be performed with relation to these elements.

GUIs are widely used to interact with any type of software application, (e.g. operating system, word-processing or information retrieval applications, spreadsheets, etc.), executed on a general-purpose computer or on a specific device (e.g. car navigation system, telephone, photocopy machine).

Documents mentioning or implying the presence of a standard GUI in the context of the disclosure of a specific software application or a specific device capable of processing data related to its specific function, should be in general classified in the appropriate subclasses related to those software applications or specific devices.

Attention is drawn to the following places, which may be of interest for search:

Hardware interface between computer and display | |

User interface programs, e.g. command shells, help systems, UIMS | |

Input/output arrangements of navigation systems | |

Program-control in industrial systems | |

Drawing of charts or graphs | |

Editing figures and text | |

Control arrangements or circuits for visual displays | |

Display of multiple viewports | |

Interaction with a remote controller on a TV display | |

End user interface for interactive television or video on demand |

In patent documents, the following abbreviations are often used:

GUI | Graphical User Interface |

In this place, the following terms or expressions are used with the meaning indicated:

Cursor (also called (mouse) pointer) | an indicator used to show the position on a computer display that will respond to input from a text input or pointing device |

Attention is drawn to the following places, which may be of interest for search:

Interaction techniques based on cursor behaviour involving tactile or force feedback | |

Interaction techniques for the selection of a displayed object |

Attention is drawn to the following places, which may be of interest for search:

Video games | |

Navigational instruments, e.g. visual route guidance using 3D or perspective road maps (including 3D objects and buildings) | |

3D image rendering in general | |

Perspective computation in 3D image rendering | |

Navigation within 3D models or images (Walk- or flight-through a virtual museum, a virtual building, a virtual landscape etc.) |

This place covers:

Documents describing icons having a specific ( or unconventional ) design or specific properties.

This place does not cover:

Graphical programming languages using iconic symbols |

Attention is drawn to the following places, which may be of interest for search:

User interfaces specially adapted for operating a cordless or mobile telephone by selecting functions from two or more displayed items, e.g. menus or icons | |

Menu-type displays in TV receivers |

This place covers:

Documents which relate to tabs.

Interaction techniques of e-books when they are heavily book-inspired.

Attention is drawn to the following places, which may be of interest for search:

Electronic books, also known as e-books |

Examples of places where the subject matter of this place is covered when specially adapted, used for a particular purpose, or incorporated in a larger system:

Edit or processing of text |

This place covers:

GUI interaction techniques specifically designed for selecting a displayed object, e.g. a window or an icon.

Selection by a pointing device (in the sense of G06F 3/03) such as a mouse, a joystick, a digitiser, etc.

This place does not cover:

Interaction with lists of selectable items, e.g. menus |

There are some older documents relating to selection by keyboard classified here. However, all new documents related to the latter are now classified in G06F 3/0489.

Every time a set of displayed of objects can be consider as structured as a "list of selectable items", the interaction technique for selecting an item should be classified in G06F 3/0482.

This place covers:

Image manipulation, e.g. dragging or rotation of the whole image, resizing of objects, changing their colour etc.

Attention is drawn to the following places, which may be of interest for search:

Image data processing or generation, in general | |

Editing figures and text; Combining figures or text |

This place covers:

Documents dealing with panning control.

In this place, the following terms or expressions are used with the meaning indicated:

Scrolling | "Dragging" in some applications, i.e. depicting a user gesture which is not causing a motion of a previously selected object, but rather a motion of a reference within a given context. |

This place covers:

Drag and drop operations comprise moving by the user a previously selected object, and finally releasing said object.

Attention is drawn to the following places, which may be of interest for search:

Interaction techniques to control scrolling |

In this place, the following terms or expressions are used with the meaning indicated:

Dragging | "Scrolling", i.e. depicting a user gesture which is not causing a motion of a previously selected object, but rather a motion of a reference within a given context. |

Attention is drawn to the following places, which may be of interest for search:

Constructional details of digitisers | |

Details of input/output arrangements of navigation systems including use of a touch screen and gestures |

Attention is drawn to the following places, which may be of interest for search:

3D input gestures | |

Handwriting per se | |

Digital ink recognition | |

Signature recognition |

This place covers:

Virtual keyboards displayed on a touchscreen or as a template on a tablet.

Attention is drawn to the following places, which may be of interest for search:

Arrangements for projecting a virtual keyboard in a portable computers | |

Character input methods like chording, prediction or disambiguation used on a keyboard | |

Programmable (hardware) keyboards | |

Entering handwritten data, e.g. gesture or text | |

Converting codes to words or guess-ahead of partial word inputs |

This place covers:

The use of keyboard keys dedicated to specific functions, e.g. <Scroll Lock>, <Home>, <PgUp> keys, as well as the use of specific combinations of keyboard keys, e.g. <Ctrl>+<A>, <Ctrl>+<C>, whereby the "+" means that the two keys have to be pressed together.

Attention is drawn to the following places, which may be of interest for search:

Selecting from displayed items by using keys for character input | |

Automatic teller machines (ATM) | |

Adjusting display parameters |

This place does not cover:

Arrangements for controlling cursor position based on coordinate signals |

Attention is drawn to the following places, which may be of interest for search:

Sample-and-hold arrangements | |

Sampling per se |

Attention is drawn to the following places, which may be of interest for search:

Error detection, error correction, monitoring per se regarding storage systems | |

Accessing or addressing within memory systems or architectures | |

Information retrieval | |

Recording or reproducing devices per se |

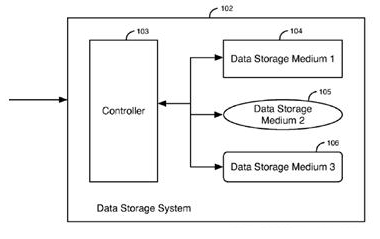

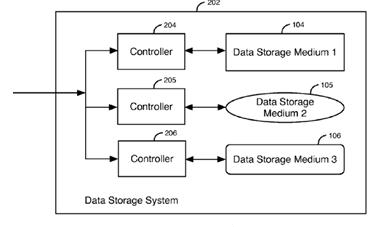

This place covers:

Physical and/or logical interfaces between a host or a plurality of hosts and a storage device or a plurality of storage devices or storage system related to data/command path and data placement techniques.

Storage devices include devices with rotating magnetic and optical storage media as well as solid state devices, or non-volatile electronic storage elements.

Interfaces to an emulated rotating storage device in (flash) memory.

Attention is drawn to the following places, which may be of interest for search:

Error detection, error correction, monitoring per se | |

Accessing, addressing or allocation within memory systems | |

Interconnection of, or transfer of information between memories, I/O devices, CPUs | |

File systems; file servers | |

Recording or reproducing devices per se | |

Cryptographic protocols | |

Network security protocols | |

Protocols for real-time services in data packet switching networks | |

Network protocols for data switching network services |

Each document should receive regarding "invention information":

- at least one classification in the range G06F 3/0602 - G06F 3/0626 for the technical effect achieved and

- at least one classification in the range G06F 3/0628 - G06F 3/0667 for the technique used and

- at least one classification in the range G06F 3/0668 - G06F 3/0689 for the infrastructure involved.

The classification of "additional information" is optional. CPC symbols in the range G06F 2206/1004 - G06F 2206/1014 should be used for classifying "additional information".

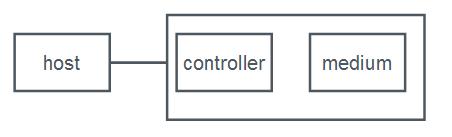

In this place, the following terms or expressions are used with the meaning indicated:

Storage system | An integrated collection of (a.) storage controllers and/or host bus adapters, (b.) storage devices such as disks, CD-ROMs, tapes, media loaders and robots, and (c.) any required control software, that provides storage services to one or more computers |

In patent documents, the following words/expressions are often used as synonyms:

- host

- computer

- PC

- PDA

- smartphone

- (micro)processor

- CPU

- terminal

- client

This place covers:

Facilitating administration like automating recurrent tasks, selecting and presenting management information to the system user or administrator.

This place covers:

Facilitating administration in relation to modification of existing systems, improving compatibility and scalability.

This place covers:

Effects leading to the reduction of the volume of data stored and the storage space requirements e.g. storage efficiency: the ratio of storage system's effective capacity to its raw capacity.

This group is often combined with the technique G06F 3/0641: data de-duplication.

This place covers:

Reducing I/O operation latency time, i.e. the time between the making of an I/O request and the completion of the request's execution.

This place covers:

Increasing I/O operation throughput, i.e. the number of I/O requests satisfied in a given time e.g. expressed in I/O requests/second (IOPS).

This place covers:

Only reliability effects with a technique specific for G06F 3/06 should be classified in this subgroup range.

Attention is drawn to the following places, which may be of interest for search:

Error detection or correction of the data by redundancy in operations | |

Redundancy in hardware using active fault-masking |

This place covers:

Increasing the life expectancy measured in e.g. Mean Time Between Failures (MTBF)

Attention is drawn to the following places, which may be of interest for search:

User address space allocation in block erasable memory: | |

Auxiliary circuits for EPROMs: |

The subject covered by this group is often described in relation to non-volatile semiconductor memory (arrays), which are, as peculiar storage infrastructure, also classified in G06F 3/0679 or G06F 3/0688

This place covers:

Increasing availability, i.e. the amount of time the system is available during those time periods it is expected to be available, measured in e.g. hours of downtime in a year.

Attention is drawn to the following places, which may be of interest for search:

Error detection or correction of the data by redundancy in operations | |

Redundancy in hardware using active fault-masking: |

This place covers:

Avoiding data to be altered or lost in operation or by accident.

Attention is drawn to the following places, which may be of interest for search:

Adding special bits or symbols to the coded information in memories: | |

Point-in-time backing up or restoration of persistent data | |

Redundancy in hardware by mirroring: | |

Error detection or correction in digital recording or reproducing: |

Attention is drawn to the following places, which may be of interest for search:

Protecting data against unauthorised access or modification | |

Protecting computer components used for data storage | |

Arrangements for network security |

This place covers: